Chip Services

Chip Services

Products

Products

- Automotive and Industrial control

- Information Security

- Edge Computing& Network Communication

Products

Resources

Resources

Language

Language

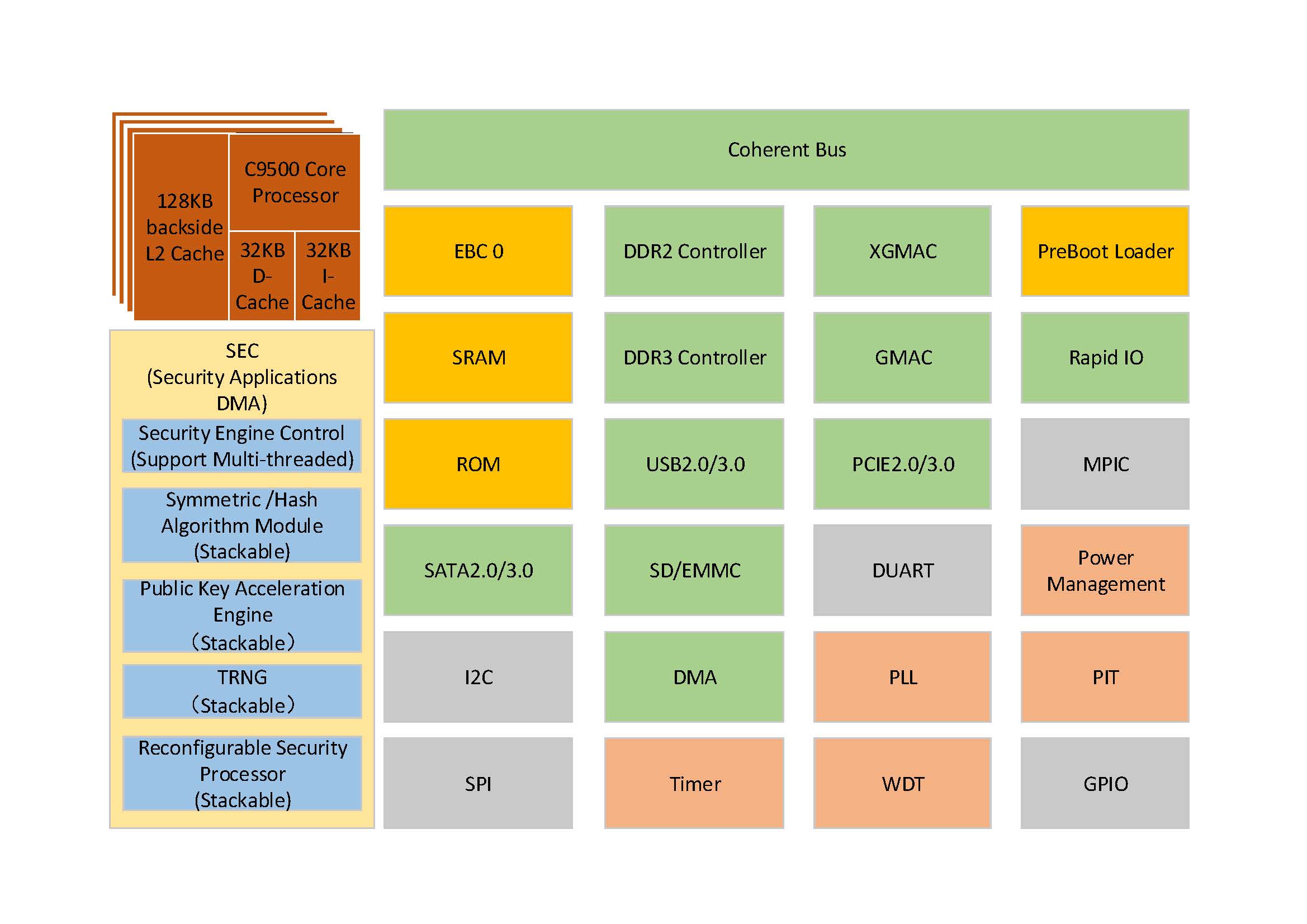

The network communication and edge computing chip design platform CSOC9500 is based on C*Core’s 32-bit high-performance information security processor C9500 with independent intellectual property rights. It supports the ISA V2.05 instruction set architecture and is compatible with the NXP E500MC. Based on the platform, the chips can be designed with multi-core processors, multiple high-speed interfaces such as 10 Gigabit Ethernet, PCIE 3.0, USB 3.0, DDR, RapidIO, etc. It provides GM cryptography algorithms and international mainstream cryptography algorithm IP, integrates multiple anti-attack protection methods, and common communication interface IP. The security chip designed based on this platform is mainly used in industrial control, system control, trusted computing and other fields.

Typical application

The H2040 high-performance embedded 32-bit processor uses a quad-core PowerPC processor with the C9500 architecture, including high-performance datapath interface logic, network, and peripheral bus interfaces which can be used for network interconnection, telecommunications/data communication, and wireless infrastructure applications.

H2040 can be used for integrated control, data path, and application layer processing in routers, switches, base station controllers, and general embedded computing. Compared to multiple discrete devices, its high integration provides significant performance advantages and greatly simplifies the design of circuit boards.

The chip operates at a standard frequency of 1200MHz and integrates high-speed interfaces such as GMAC, PCIE, and DDR.

H2040 can operate with temperature of -40 to 125℃.

● Independent 32-KB L1-cache and 32-KB L2-cache for each core.

● Dedicated 128kB L2 cache for each core.

● Supports 3 levels of instructions: user, supervisor, and hypervisor.

● Independent boot and reset mechanisms.

● ROM/SRAM

● PCIE3/USB3/USB2/

SATA2/SATA3/SRIO2/RapidIO

● SD/eMMC

● SPI/I2C/UART/MPIC

● 4 JobRings for algorithm scheduling.

● Public Key Algorithm acceleration engine:

- Supporting Diffie Hellman/SM2/SM9/ECC/RSA.

● Symmetric algorithm acceleration engine:

- Supporting SM1/SM4/SM6/SSF33/AES/DES/3DES.

● Hash algorithm acceleration engine:

- Supporting SM3/MD5/HMAC/SHA0/SHA1/SHA2(224/256/384/512).

● Reconfigurable symmetric Cryptographic algorithm acceleration processor(RSCP).

● TRNG.

● CRC accelerator.

● Anti-side-channel attacks.

● Completing complex application flows independently .

● Supporting all mainstream public key algorithms (RSA/ECC/SM2/SM9).

● Supporting up to 4096-bit modular operations.

● Supporting 1024-bit elliptic curve operations (prime field/binary field).

● Supporting Miller-Rabin primality testing algorithm.

● Supporting encryption/decryption, signature verification, and secret derivation.

● Supporting secret key generation (DSA/ECDSA/DH/ECDH, etc.).

● Dedicated 256-bit instruction set for symmetric algorithms.

● Harvard architecture.

● Supporting most symmetric algorithms:

- Block cipher algorithms/stream cipher algorithms/hash cipher algorithms.

● Operating independently or tightly coupled with SEC.

● Supporting secure memory of algorithm programs.

● 256-bit random number generation.

● Internal random number seed generation.

● Internal seed can be automatically updated periodically.

● Optional dedicated random number control and access interface, easy for direct invocation by other modules.

● Generates 256bits random numbers in 1024 clock cycles, i.e., 1bit per 4 clock cycles.

● 32-bit ultra-low power processor.