Chip Services

Chip Services

Products

Products

- Automotive and Industrial control

- Information Security

- Edge Computing& Network Communication

Products

Resources

Resources

Language

Language

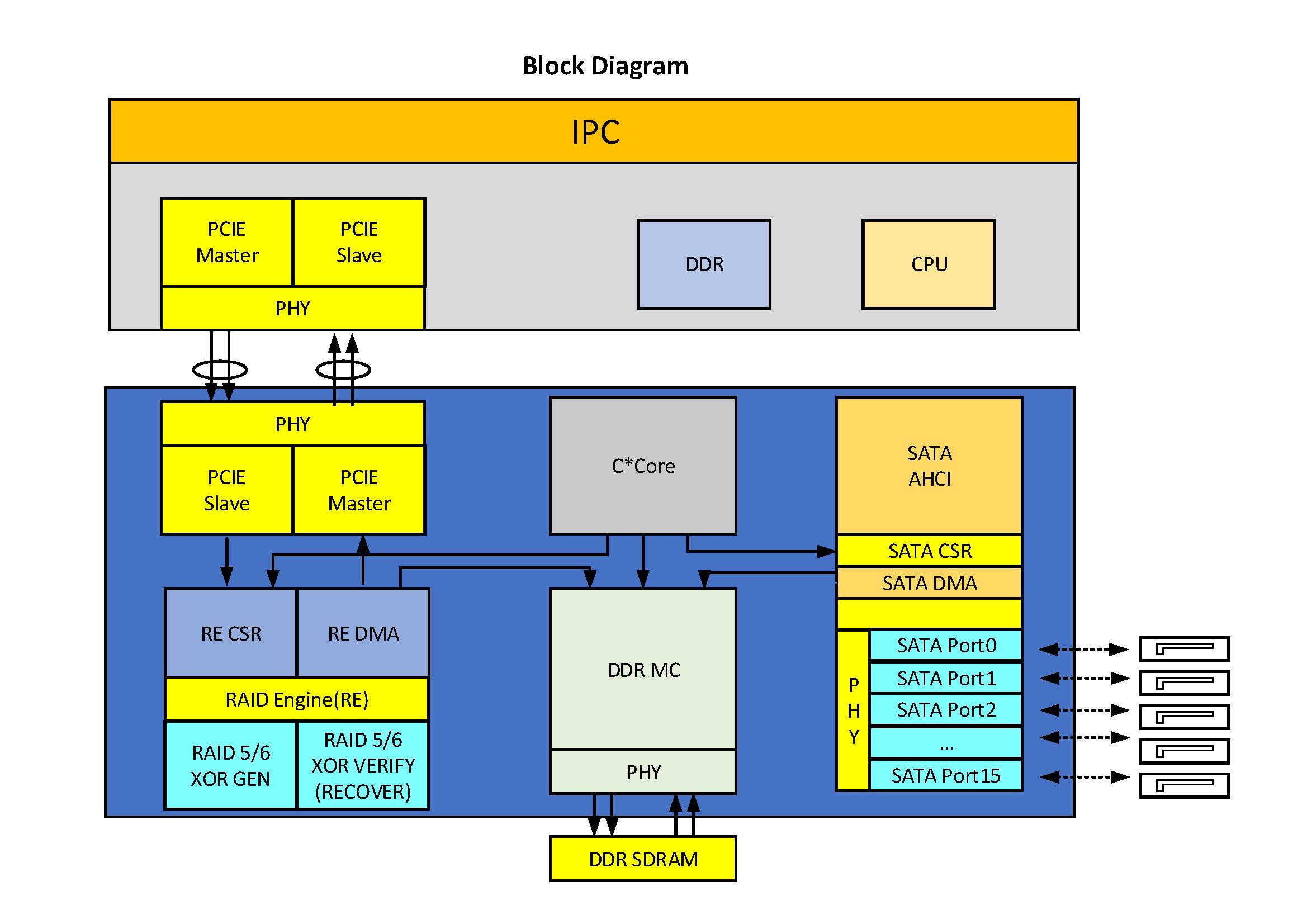

The CCRD3316 is a RAID controller chip, integrated with C0 and C8000 cores of C*Core, for disk array controlling especially for server storage array applications with multiple independent SATA protocol of 4.0 interface channels. . The chip supports both mechanical hard drives and SSD solid-state storage drives with PCIE3.0 standard protocol interface channels enabling highly reliable and high-performance data transmission.

A disk array consists of multiple independent disks which constitute a single massively capacious disk group. It leverages the synergistic effects of individual disks to enhance the overall performance of the disk system. With this technology, data is segmented into numerous sections and stored separately on each hard disk.

The chip normally operates at a frequency of 500MHz with high-speed interfaces such as SATA, DDR, and PCIE.

The CCRD3316 chip is manufactured using the process of 28 nm and can operate at the temperature range of -40 to 125℃.

• C0 core、C8000 core

• Fast Interrupt Response

• Peripheral Access Interface

• Compatible with PCIE Gen1/2 standards

• 64-bit addressing space with a maximum of 4GB

• Supporting configurable receiving buffers (256 Bytes or 16K Bytes)

• Supporting MSI (Message-Signaled Interrupts)

• Supporting descriptor-based control for transmission and reception (utilizing DMA Link List Mode)

• Supporting software reset

• Peak throughput of 12GB/s

• 72-bit interface

• Supporting NCQ (Native Command Queuing) and AHCI (Advanced Host Controller Interface) protocol

• DMA read/write support

• Supporting Link-List mode for automatic command execution

• Automatically transfers data from DDR to PCIE

• Hardware instruction descriptor commands

• Hardware generating SATA commands

• Hardware handling handshaking with the host computer through PCIE

• Hardware computing RAID-related checksum values

• Hardware replying with data using checksum values

• Hareware generating multi-disk address information

• I2C (IIC bus interface)

• UART (Universal Asynchronous Receiver Transmitter)

• GPIO (General Purpose Input/Output)

• SGPIO

• SPI

• EMMC

• SSI

• 2MBAXI SRAM

• PCIe subsystem supports ASPM power management mechanism

• The entire system is synchronous design

• Five phase-locked loops (PLLs) provide separate clocks

• Distinct high-speed clocks supply for each of the subsystem of C0, C8000, DDR Master, DDR AXI, PCIE AXI, SATA AXI, EMMC and BUS AXI

• Distinct low-speed clocks supply for SSI and UART

• The system supports global POR (Power-On Reset)